대만 TSMC의 3나노미터 공정이 논란의 중심에 섰다. 5나노로 생산한 SRAM과 비교해 반도체 셀 면적이 큰 차이가 없다는 사실이 드러나서다. TSMC의 악재가 지속되며 삼성전자가 '만년 2위'를 탈출할 기회를 잡을 것이라는 분석이 나온다.

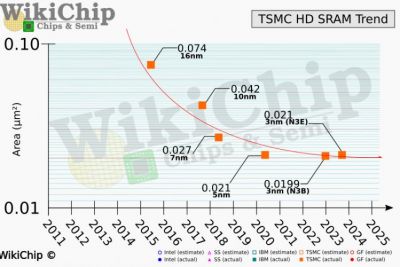

반도체 전문 매체 위키칩(WiKi Chip)은 지난 14일(현지시간) TSMC가 'IEEE 국제전자소자학회(IEDM) 2022'에서 발표한 내용을 인용해 "3나노 기반 SRAM은 이전 제품 대비 공정 미세화(Scailing)의 진전이 없다"고 보도했다.

TSMC의 3나노 1세대(N3) 공정에서 생산된 SRAM은 반도체 셀 면적이 0.0199마이크로평방미터(µm²·1μm²는 100만분의 1m²)로 5나노 기반의 칩(0.021µm²)보다 불과 5% 작다. 3나노 2세대(N3E) 제품과 비교하면 면적이 동일하다.

면적에 큰 차이가 없어 전체 제품에서 SRAM이 차지하는 비중도 크게 줄지 않을 전망이다. 위키칩은 다이 크기가 255mm²로 SRAM이 45mm²(17.6%)를 차지하는 칩을 3·5나노로 제작했을 때를 가정해 SRAM의 비중을 비교했다. 3나노 공정을 적용하면 다이 크기는 44mm²로 SRAM은 거의 30%(12.58mm²)를 차지했다. 5나노로 만들었을 때와 비교해 SRAM의 비중(22.5%)은 더 높다.

TSMC는 SRAM의 면적을 획기적으로 줄일 수 있는 진보된 N3S 공정을 개발하고 있다. 다만 N3S 칩은 2024년에야 생산될 전망이어서 당분간 TSMC의 3나노 공정은 5나노 대비 경쟁력이 없을 것으로 보인다.

가뜩이나 TSMC는 수율 문제로 3나노 공정 양산에 어려움을 겪고 있다.

TSMC가 경쟁력을 잃는 사이 삼성은 세계 최초로 3나노 공정 양산에 성공하고 여러 고객사로부터 러브콜을 받고 있다. 삼성전자 파운드리 사업부는 엔비디아와 퀄컴, IBM, 바이두 등을 3나노 고객으로 확보했다.

삼성 GAA 3나노 수율 50% 돌파

TSMC 3나노, 미세화 경쟁력 없어 삼성 파운드리, 우위 점하나

139

ツイートLINEお気に入り 104

104 28

28